# cādence°

## Gigabit Ethernet MAC (GEM)

## **Technical Data Sheet**

Part Number: T-CS-ET-0005-100

Document Number: I-IPA01-0099-USR Rev 26

January 2012

## **Gigabit Ethernet MAC (GEM)**

©2002-2012 Cadence Design Systems, Inc. All rights reserved

#### **Proprietary Notice**

In the U.S. and numerous other countries, Cadence and the Cadence logo are registered trademarks and Cadence Design Foundry is a trademark of Cadence Design Systems, Inc. All other products or services mentioned herein may be trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in this document may be adapted or reproduced in any material form except with the prior written permission of the copyright owner.

The product described in this document is subject to continuous developments and improvements and is supplied "AS IS". All warranties implied or expressed including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded. Cadence Design Foundry, Inc shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product. Cadence Design Foundry products are not authorized for use as critical components in life support devices or systems without the express written approval of an authorised officer of Cadence Design Foundry, Inc. As used herein:

- 1. Life support devices or systems are devices of systems that are (a) intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system or system whose failure to perform can reasonably be expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### Gigabit Ethernet MAC (GEM)

#### **MAC Features**

- UNH tested

- Compatible with IEEE Standard 802.3

- 10, 100 and 1000 Mbps operation

- Statistics counter registers for RMON/MIB

- GMII/MII/TBI interfaces supported

- Support for SGMII

- Support for RGMII included by means of the Cadence T-CS-ET-0019-100 "Reduced Gigabit Media Independent Interface block"

- Integrated 1000BASE-X physical coding sub-layer (PCS) with auto-negotiation

- Either external FIFO interface, AMBA AHB or AMBA AXI bus master direct memory access (DMA) interface to external memory

- Support for up to eight priority queues on transmit and receive

- Support for 802.1AS and 1588 precision clock synchronization protocol

- Optional IEEE 1588 time stamp unit

- Support for 802.3az Energy Efficient Ethernet

- Full duplex flow control with recognition of incoming pause frames and hardware generation of transmitted pause frames

- Support for 802.1Qbb priority-based flow control

- Half duplex flow control by forcing collisions on incoming frames

- Receive and transmit IP, TCP and UDP checksum offload. Both IPv4 (with IP options) and IPv6 (with extension headers) packet types supported

- Automatic pad and cyclic redundancy check (CRC) generation on transmitted frames

- Frame extension and frame bursting at 1000 Mbps in half duplex mode

- Address checking logic for four or thirty two specific 48 bit addresses, four type lds, promiscuous mode, external address checking, hash matching of unicast and multicast destination addresses and Wake-on-LAN

- MDIO interface for physical layer management

- Support for jumbo frames up to 10,240 bytes

- Programmable IPG stretch

- Configuration interface compatible with AMBA APB interface, version 2.0

- Interrupt generation to signal receive and transmit completion, errors and other events

- Support for 802.1Q VLAN tagging with recognition of incoming VLAN and priority tagged frames

## **Optional DMA Features**

- AHB or AXI4 compliant master interface

- Selectable low latency FIFOs or packet buffer SRAM on transmit and receive DMA

- Support for full store and forward or flexible low latency partial store and forward configurations available

- Configurable for 32 bit, 64 bit and 128 bit data paths (128 bit AXI is not supported)

- Support for Priority Queue Management to stream data to and from up to 8 independent external traffic queues

- Highly flexible and configurable screening algorithm based on VLAN, IP, TCP, UDP and other indexed packet fields to map receive frames to priority queues.

- $\circ$   $\;$  High priority traffic given precedence over lower priority traffic on TX path.

- Ability for high priority transmit traffic to be internally reordered to reduce traffic latency.

- Programmable burst length and endianism

- Automatic self completing retries for half duplex operation

- Optional automatic discard of frames received with MAC related errors

- Optional support for manual or automatic flushing of frames received when external memory resource has been exhausted or AHB/AXI access errors occur

- Options to help maximize burst efficiency

## Description

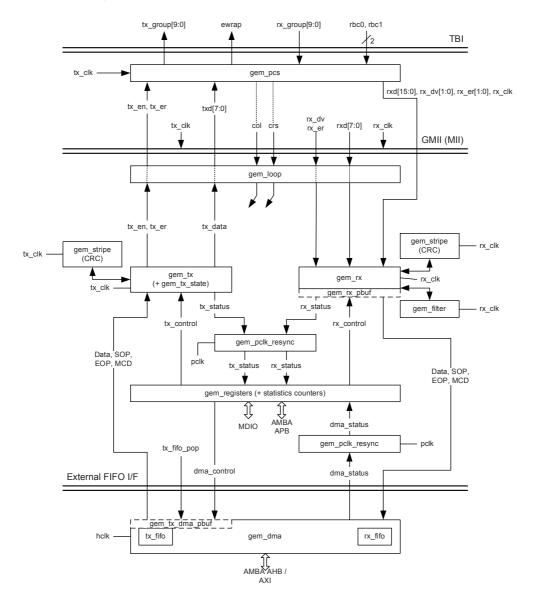

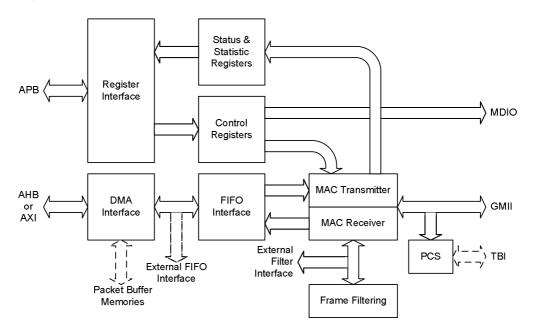

The Gigabit Ethernet MAC (GEM) module implements a 10/100/1000 Mbps Ethernet MAC compatible with the IEEE 802.3 standard. The GEM can operate in either half or full duplex at all three speeds. The network configuration register is used to select the speed, duplex mode and interface type (MII, GMII, RGMII, TBI or SGMII).

The GEM comprises five constituent components:

- GEM\_MAC controlling transmit, receive, address checking and loopback

- GEM\_REG\_TOP providing control and status registers, statistics registers and synchronization logic

- GEM\_PCS controlling the 8B/10B encoder, 8B/10B decoder, PCS transmit, PCS receive and PCS auto-negotiation

- GEM\_DMA\_TOP controlling DMA transmit, DMA receive and AHB/AXI arbitration logic

- GEM\_TSU calculates the IEEE 1588 timer values

In system applications where no DMA operation is required, the GEM\_DMA\_TOP module can be removed using a compile option and an external FIFO interface used to incorporate the GEM into a SoC environment. Similarly, the GEM\_PCS module may be removed using a compile option.

#### **GEM\_MAC**

The MAC transmit block takes data from the external FIFO interface, adds preamble and, if necessary, pad and frame check sequence (FCS). Both half duplex and full duplex Ethernet modes of operation are supported. When operating in half duplex mode, the MAC transmit block generates data according to the carrier sense multiple access with collision detect (CSMA/CD) protocol. The start of transmission is deferred if carrier sense (crs) is active. If collision (col) becomes active during transmission, a jam sequence is asserted and the transmission is retried after a random back off. The crs and col signals have no effect in full duplex mode. When operating in gigabit mode half duplex, both carrier extension and frame bursting are performed in accordance with the IEEE 802.3 standard.

The MAC receive block checks for valid preamble, FCS, alignment and length, and presents received frames to the MAC address checking block and external FIFO interface. Software can configure the GEM to receive jumbo frames up to 10,240 bytes. It can optionally strip CRC from the received frame prior to transfer to the external FIFO interface.

The address checker recognizes four specific 48 bit addresses, can recognize four different type ID values, and contains a 64 bit hash register for matching multicast and unicast addresses as required. It can recognize the broadcast address of all ones, copy all frames and act on external address matching signals. The MAC can also reject all frames that are not VLAN tagged and recognise Wake on LAN events. Address comparison against individual bits of Specific Address Register 1 can be masked by means of the Specific Address Mask Register.

The MAC receive block supports offloading of IP, TCP and UDP checksum calculations (both IPv4 and IPv6 packet types supported), and can automatically discard bad checksum frames.

#### GEM\_PCS

A PCS sub-layer is incorporated for 1000 Mbps operation and provides a TBI to the PMA layer. A PCS transmit module and 8B/10B encoder form the transmit path, and a PCS receiver and two 8B/10B decoders form the receive path, which is expanded into 16 bits to simplify clocking. Auto-negotiation is also provided for network configuration.

The PCS can be configured through the network configuration register to support an SGMII interface between the MAC and an external PHY. For a complete SGMII solution a SerDes hard macro is also required.

#### GEM\_REG\_TOP

Control registers drive the management data input/output (MDIO) interface, set-up DMA activity, start frame transmission and select modes of operation such as full duplex, half duplex and 10/100/1000 Mbps operation. The register interface is compatible with the AMBA APB bus standard. Where possible, register set compatibility has been maintained with the Ethernet MAC 10/100 (Enhanced) and the 10 Gigabit Ethernet MAC (XGM) from Cadence.

The statistics register block contains registers for counting various types of event associated with transmit and receive operation. These registers, along with the status words stored in the receive buffer list, enable software to generate network management statistics compatible with IEEE 802.3 clause 30.

#### GEM\_DMA\_TOP

The DMA may be configured in either a very low latency buffering mode using internal transmit and receive FIFOs or a packet buffering mode using external memories.

Data path bus widths of 32 bit, 64 bit and 128 bit are supported at all data rates (128 bit AXI is not supported), although system designers should carefully consider the bandwidth requirements of the external data path being used — either external FIFO interface or AMBA AHB/AXI interface. The DMA block connects to external memory through its AMBA AHB or AXI bus interface. The DMA loads the transmit buffer and empties the receive buffer using bus master operations. Receive data is not sent to memory until the address checking logic has determined that the frame should be copied.

Receive or transmit frames are stored in one or more DMA buffers. The receive buffer size is programmable between 64 bytes and 16 Kbytes. Transmit buffers range in length between 1 and 2047 bytes, and up to 128 buffers are permitted per frame. The DMA block manages the transmit and receive frame buffer queues.

For chip architecture where DMA is not required, the GEM is supplied with an external transmit and receive external FIFO interface, thus simplifying design complexity and reducing gate count.

Note the DMA block does not use AMBA AHB split and retry operations.

#### GEM\_TSU

The 1588 time stamp unit (TSU) is a timer implemented as a 62 bit register. The 32 upper bits count seconds and the 30 lower bits count nanoseconds. The 30 lower bits roll over when they have counted to one second. The timer increments by a programmable number of nanoseconds with each PCLK period and can be adjusted (incremented or decremented) through APB register accesses.

Module Data

## **Block Diagram**

#### **Signal Interfaces**

The GEM includes the following signal interfaces:

- GMII, MII, and TBI to an external PHY

- MDIO interface for external PHY management

- AMBA Advanced Peripheral Bus (APB) slave interface for accessing the GEM's registers

- AMBA Advanced High Speed Bus (AHB or AXI4) master interface for memory access

- An optional FIFO interface in applications where DMA functionality is not required

- An optional packet buffer memory interface for the DMA

The AMBA interfaces fully conform to the ARM AMBA Revision 2.0 specification.

#### Ethernet Interface (GMII/MII)

| Signal Name | I/O | Description                                                                                                                  |

|-------------|-----|------------------------------------------------------------------------------------------------------------------------------|

| col         | Ι   | Collision detect from the PHY.                                                                                               |

| crs         | Ι   | Carrier sense from the PHY.                                                                                                  |

| tx_er       | 0   | Transmit error signal to the PHY. Asserted if the DMA<br>block fails to fetch data from memory during frame<br>transmission. |

| txd[7:0]    | 0   | Transmit data to the PHY.<br>10/100 mode: txd[3:0] used, txd[7:4] tied to logic 0.<br>1000 mode: txd[7:0] used.              |

| tx en       | 0   | Transmit enable to the PHY.                                                                                                  |

| tx clk      | Ι   | Transmit clock from the system clock generator.                                                                              |

| rxd[7:0]    | Ι   | Receive data from the PHY:<br>10/100 mode: rxd[3:0] used, rxd[7:4] not used.<br>1000 mode: rxd[7:0] used.                    |

Module Data

| rx_er            |   | Receive error signal from the PHY.                                                                                                                                                                                                                                     |

|------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx clk           | Ι | Receive clock from the system clock generator.                                                                                                                                                                                                                         |

| rx dv            | Ι | Receive data valid signal from the PHY.                                                                                                                                                                                                                                |

| mdc              | 0 | Management data clock to pin.                                                                                                                                                                                                                                          |

| mdio in          | Ι | Management data input from MDIO pin.                                                                                                                                                                                                                                   |

| mdio out         | 0 | Management data output to MDIO pin.                                                                                                                                                                                                                                    |

| mdio_en          | 0 | Management data output enable to MDIO pin. At the top-level the three mdio pins are all used to drive a single tri-sate pin. Alternatively MDIO may be implemented as a pull-down. In this case the enable to the pull-down should be driven with ~mdio_out & mdio_en. |

| ext interrupt in | Ι | External interrupt input pin.                                                                                                                                                                                                                                          |

#### **Control/Status Interface**

| Signal Name     | l/<br>O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| loopback        | 0       | Selects external loopback — not used by most PHYs.<br>This signal does not need to be bonded out, but is used<br>by the testbench.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| loopback_local  | 0       | Internal loopback indication to the system clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| half_duplex     | 0       | Selects half duplex — this signal does not need to be bonded out, but is used by the testbench.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| speed_mode[2:0] | 0       | Indicates speed and external interface that the GEM is<br>currently configured to use to the system clock<br>generator:<br>000 - 10 Mbps Ethernet operation using MII interface<br>001 - 100 Mbps operation using MII interface<br>01x - 1000 Mbps operation using GMII interface<br>100 - 10 Mbps operation using SGMII interface<br>101 - 100 Mbps operation using SGMII interface<br>11x - 1000 Mbps operation using TBI or SGMII interface                                                                                                                                                      |

| tx_pause        | 1       | Toggle input for pause frame transmission.<br>When $tx\_pfc\_sel$ is LOW, a classic 802.3 pause<br>frame will be transitted. The pause quantum value to be<br>transmitted depends on the state of the $tx\_pause\_zero$<br>pin.<br>When $tx\_pfc\_sel$ is HIGH, an 802.1Qbb, or PFC<br>priority based pause frame will be transmitted. The<br>pause quantum value to be transmitted depends on the<br>state of the $tx\_pfc\_priority$ bus.<br>Tie this input low if hardware initiated flow control is not<br>being used.<br>This asynchronous input is synchronized into the $tx\_clk$<br>domain. |

| tx_pfc_sel      | I       | Indicates whether the pause frame to be transmitted<br>should be classic 802.3 (when set to logic 0) or PFC<br>priority based pause frame (when set to logic 1). This<br>signal should be valid when tx_pause toggles and                                                                                                                                                                                                                                                                                                                                                                           |

| tx_pause_zero              | 1 | remain valid for at least two tx_clk cycles afterwards.<br>Tie this low if hardware initiated flow control is not being<br>used.<br>Indicates whether the classic 802.3 pause frame to be<br>transmitted is to have zero pause quantum (when set to<br>logic 1) or the value of the transmit pause quantum<br>register (when set to logic 0). This signal should be valid<br>when tx_pause toggles and remain valid for at least two<br>tx_clk cycles afterwards.<br>Tie this low if hardware initiated flow control is not being<br>used. |

|----------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_pfc_pause[7:0]          | Ι | Indicates the value to be used in the 8bit priority enable vector of the PFC priority based pause frame. This signal should be valid when tx_pause toggles and remain valid for at least two tx_clk cycles afterwards. Tie this low if hardware initiated flow control is not being used.                                                                                                                                                                                                                                                  |

| tx_pfc_pause_zero<br>[7:0] | Ι | Indicates whether each priority entry in the PFC priority<br>based pause frame is to have zero pause quantum<br>(when set to logic 1) or the value of the transmit pause<br>quantum register (when set to logic 0). This signal<br>should be valid when tx_pause toggles and remain valid<br>for at least two tx_clk cycles afterwards.<br>Tie this low if hardware initiated flow control is not being<br>used.                                                                                                                           |

| trigger_dma_tx_sta<br>rt   | I | Toggle input for starting transmit DMA.<br>Only present when using the DMA configured for<br>internal packet buffering. This signal is used as a<br>hardware alternative to setting the TX START bit of the<br>network control register.<br>If the user only wishes to use software to initiate<br>transmission, then this input can be tied low.<br>This asynchronous input is synchronized into the hclk<br>domain                                                                                                                       |

| rx_pfc_paused[7:0]         | 0 | Each bit corresponds to a priority indicated within the<br>PFC priority based pause frame.<br>Each bit is set when an PFC priority based pause frame<br>has been received, and the associated priority pause<br>time quantum is non-zero. Each bit is cleared when the<br>associated pause time identified by the received pause<br>time quantum has elapsed.                                                                                                                                                                              |

| pfc_negotiate              | 0 | <ul> <li>Identifies that PFC priority based pause flow control has been negotiated.</li> <li>No PFC priority based pause frames have yet been received, flow control is being handled using classic 802.3 pause frames.</li> <li>At least one PFC priority based pause frames has been received. All subsequent 802.3 pause frames will be dropped.</li> </ul>                                                                                                                                                                             |

| rx_databuf_wr_q0           | 0 | When priority queueing is disabled, this output is toggled on a DMA write to the first word of each DMA data buffer. When priority queueing is enabled, this                                                                                                                                                                                                                                                                                                                                                                               |

|                                |   | output is toggled on a DMA write to the first word of each DMA data buffer associated with queue 0.                                                                                                                                                                                                                    |

|--------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_databuf_wr_q1               | 0 | Only present when priority queueing support is enabled.<br>This output is toggled on a DMA write to the first word of<br>each DMA data buffer associated with queue 1.                                                                                                                                                 |

| rx_databuf_wr_q2               | 0 | Only present when priority queueing support is enabled.<br>This output is toggled on a DMA write to the first word of<br>each DMA data buffer associated with queue 2.                                                                                                                                                 |

| halfduplex_flow_co<br>ntrol_en | Ι | Asynchronous Input.<br>This input is ignored when the GEM is configured for full<br>duplex or gigabit modes.<br>Setting this bit high will enable the half duplex flow<br>control mechanism. The transmit block will transmit 64<br>bits of data, whenever it sees an incoming frame in<br>order to force a collision. |

| dma_bus_width[1:0]             | 0 | Indicates width of DMA or external FIFO data bus as<br>follows— this signal does not need to be bonded out,<br>but is used by the testbench:<br>00 - 32 bit data bus<br>01 - 64 bit data bus<br>10 or 11 - 128 bit data bus.                                                                                           |

#### **External Filter Interface**

| Signal Name                                          | I/O | Description                                                                                                                                                                                                                      |

|------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ext_match1<br>ext_match2<br>ext_match3<br>ext_match4 | Ι   | Optional external match 1, 2, 3 and 4 — any one of these input signals from the external filter logic can be asserted indicating a match was found. Filter matches can take place on either ext_sa, ext_da, ext_type or ext_vid. |

| ext_sa[47:0]                                         | 0   | Source address for comparison, extracted from packet being received.                                                                                                                                                             |

| ext_sa_stb                                           | 0   | Validates source address.                                                                                                                                                                                                        |

| ext_da[47:0]                                         | 0   | Destination address for comparison, extracted from packet being received.                                                                                                                                                        |

| ext_da_stb                                           | 0   | Validates destination address.                                                                                                                                                                                                   |

| ext_type[15:0]                                       | 0   | Length/type field for comparison, extracted from packet being received.                                                                                                                                                          |

| ext_type_stb                                         | 0   | Validates length/type field.                                                                                                                                                                                                     |

| ext_vlan_tag1[31:<br>0]                              | 0   | VLAN identifier and VLAN ID field for comparison,<br>extracted from packet being received. For packets<br>incorporating 2 VLAN tags (stacked VLAN), this<br>represents the first VLAN tag                                        |

| ext_vlan_tag1_stb                                    | 0   | Validates VLAN ID field.                                                                                                                                                                                                         |

| ext_vlan_tag2[31:<br>0] | 0 | VLAN identifier and VLAN ID field for comparison,<br>extracted from packet being received. For packets<br>incorporating 2 VLAN tags (stacked VLAN), this<br>represents the second VLAN tag. These bits are only<br>valid for packets incorporating the stacked VLAN<br>processing feature. |

|-------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ext_vlan_tag2_stb       | 0 | Validates VLAN ID field.                                                                                                                                                                                                                                                                   |

| ext_ip_sa[127:0]        | 0 | IP source address for comparison, extracted from the packet being received. For IPv4 packets, only bits [31:0] are valid. For Ipv6 packets, bits [127:0] are vaid.                                                                                                                         |

| ext_ip_sa_stb           | 0 | Validates IP source address field.                                                                                                                                                                                                                                                         |

| ext_ip_da[127:0]        | 0 | IP destination address for comparison, extracted from<br>the packet being received. For IPv4 packets, only bits<br>[31:0] are valid. For Ipv6 packets, bits [127:0] are vaid.                                                                                                              |

| ext_ip_da_stb           | 0 | Validates IP destination address field.                                                                                                                                                                                                                                                    |

| wol                     | 0 | Asserted for 64 rx_clk cycles if a magic packet, ARP request, specific address 1 or multicast hash event is decoded and is enabled through the Wake on LAN register. Only bond this pin out if Wake on LAN functionality is required.                                                      |

## IEEE 1588 PTP frame recognition and Time Stamp Unit

| Signal Name    | I/O | Description                                                                                                  |

|----------------|-----|--------------------------------------------------------------------------------------------------------------|

| sof_tx         | 0   | Asserted high synchronous to tx_clk when the SFD is detected on a transmit frame, deasserted at end of frame |

| sync_frame_tx  | 0   | Asserted high synchronous to tx_clk if PTP sync frame is detected on transmit.                               |

| delay_req_tx   | 0   | Asserted high synchronous to tx_clk if PTP delay request frame is detected on transmit.                      |

| pdelay_req_tx  | 0   | Asserted high synchronous to tx_clk if PTP peer delay request frame is detected on transmit.                 |

| pdelay_resp_tx | 0   | Asserted high synchronous to tx_clk if PTP peer delay response frame is detected on transmit.                |

| sof_rx         | 0   | Asserted high synchronous to rx_clk when the SFD is detected on a receive frame                              |

| sync_frame_rx  | 0   | Asserted high synchronous to rx_clk if PTP sync frame is detected on receive.                                |

| delay_req_rx   | 0   | Asserted high synchronous to rx_clk if PTP delay request frame is detected on receive.                       |

| pdelay_req_rx  | 0   | Asserted high synchronous to rx_clk if PTP peer delay request frame is detected on receive.                  |

| pdelay_resp_rx | 0   | Asserted high synchronous to rx_clk if PTP peer delay response frame is detected on receive.                 |

| tsu_clk                   | Ι | Alternative clock source for the time stamp unit. If gem_tsu_clk is defined in the gem_defs.v file then the TSU is clocked by tsu_clk rather than pclk. Must run slower than pclk. |

|---------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gem_tsu_ms                | Ι | TSU master/slave. Used with gem_tsu_inc_ctrl to control incrementing of the TSU and loading the sync strobe register.                                                              |

| gem_tsu_inc_ctrl[<br>1:0] | I | Used to control incrementing of the TSU and<br>synchronous to tsu_clk or pclk. Drive high when not<br>being used.                                                                  |

| tsu_timer_cnt[61:<br>0]   | 0 | TSU timer count value, synchronized to tsu_clk or pclk.<br>Upper 32 bits are seconds value and lower 30 bits are<br>nanoseconds.                                                   |

| tsu_timer_cmp_val         | 0 | TSU timer comparison valid, synchronized to tsu_clk or<br>pclk. Asserted high when upper 54 bits of TSU timer<br>count value are equal to programmed comparison<br>value.          |

## Ethernet Interface (TBI)

| Signal Name   | I/O | Description                                                                                                                                                                                                                                                      |

|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_group[9:0] | 0   | 8B/10B encoded transmit data to PHY transceiver, synchronized to tx_clk.                                                                                                                                                                                         |

| gtx_clk       | I   | 125 MHz PCS transmit clock. In non-SGMII application this will have the same source as $tx_clk$ . In SGMII applications gtx_clk is supplied to the PCS at 125MHZ but divided down to drive $tx_clk$ at 10 and 100Mb/s speeds                                     |

| rx_group[9:0] | I   | 8B/10B encoded receive data from PHY transceiver.                                                                                                                                                                                                                |

| rbc0<br>rbc1  | I   | Receive clocks from PHY transceiver, rbc1 will be 180 degrees phase shifted with respect to rbc0.                                                                                                                                                                |

| ewrap         | 0   | Control for loopback operation in the PHY transceiver.                                                                                                                                                                                                           |

| en_cdet       | 0   | Control for comma alignment in the PHY transceiver (see IEEE 802.3 subclause 36.3.2.4). Leave unconnected if an on-chip SerDes is being used.                                                                                                                    |

| signal_detect | I   | Valid signal detected from PMA. This signal must be driven<br>high for PCS synchronization to occur. Users are advised<br>to check that this signal is driven high by their SerDes or to<br>provide a control signal to over-ride the signal from the<br>SerDes. |

#### Signals for optional on chip SerDes

These signals will only be present if the GEM has been configured to support comma alignment.

| Signal Name | I/O | Description                                                                                                                                                                |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pma_rx_clk  | I   | 125MHz recovered clock from the SerDes. This clock is used by the comma alignment module.                                                                                  |

| n_prxreset  | I   | Active low pma_rx_clk domain reset. This signal should be asserted low asynchronously, and deasserted high synchronously with pma_rx_clk.                                  |

| rbc_align   | 0   | Used in clock control block to align the rbc clocks correctly to even and odd code groups. This signal is asserted for a single pma_rx_clk cycle when a comma is detected. |

#### Interrupt Controller Interface

| Signal Name  | I/O | Description                                    |

|--------------|-----|------------------------------------------------|

| ethernet_int | 0   | Ethernet interrupt signal synchronous to pclk. |

## **External Transmit FIFO Interface**

| Signal Name      | I/O | Description                                                                                                                                                                                                     |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_r_data_rdy    | I   | When set to logic 1, indicates enough data is present in the external FIFO for Ethernet frame transmission to commence on the current packet.                                                                   |

| tx_r_rd          | 0   | Single $tx_clk$ clock cycle wide active high output<br>requesting a word (either 32-bits, 64-bits or 128-bits) of<br>information from the external FIFO interface.<br>Synchronous to the $tx_clk$ clock domain. |

| tx_r_valid       | I   | Single tx_clk clock cycle wide active high input<br>indicating requested FIFO data is now valid. Validates<br>the following inputs: tx_r_data[127:0], tx_r_sop,<br>tx_r_eop, tx_r_err and tx_r_mod[3:0].        |

| tx_r_data[127:0] | I   | FIFO data for transmission, either 32-bit, 64-bit or 128-bit depending on $dma\_bus\_width[2:0]$ which is configured through the register interface. This input is only valid whilst $tx\_r\_valid$ is high.    |

| tx_r_sop         | I   | Start of packet, indicates the word received from the external FIFO interface is the first in a packet. This input is only valid whilst tx_r_valid is high.                                                     |

| tx_r_eop         | I   | End of packet, indicates the word received from the external FIFO interface is the last in a packet. This input is only valid whilst tx_r_valid is high.                                                        |

| tx_r_mod[3:0]  | I | Read module, indicates how many bytes are valid on<br>tx_r_data during the last transfer of the packet:<br>0000- all bytes are valid<br>0001 - tx_r_data[7:0] is valid<br>0010 - tx_r_data[15:0] is valid<br>0011 - tx_r_data[23:0] is valid, and so on until<br>1111 - tx_r_data[119:0] is valid.<br>This input is only valid when both tx_r_eop and<br>tx_r_valid are high. |

|----------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_r_err       | I | Error, active high input indicating the current packet contains an error. This signal is only valid whilst tx_r_valid is high and may be set at any time during the packet transfer.                                                                                                                                                                                          |

| tx_r_underflow | I | FIFO under flow, indicating the transmit FIFO was empty<br>when a read was attempted. This signal is only valid<br>when the GEM has attempted a read by asserting tx_r_rd<br>and the tx_r_valid signal has not yet been indicated.<br>tx_r_flushed should be asserted following this event to<br>indicate to the GEM when it is safe to resume reading.                       |

| tx_r_flushed   | I | This signal must be driven high and then low after a major<br>error event to indicate to GEM that the external FIFO has<br>been flushed. This will enable the GEM to resume<br>reading data.<br>Events that require this to be set are indicated by any bit<br>of $tx_rstatus$ being asserted                                                                                 |

| tx_r_control   | I | $tx\_no\_erc$ , set active high at start of packet to indicate<br>current frame is to be transmitted without erc being<br>appended. This input is only valid whilst both $tx\_r\_valid$<br>and $tx\_r\_sop$ are high.                                                                                                                                                         |

*Note:* The transmit FIFO interface inputs must be pre-synchronized to the tx\_clk clock domain.

## **External Transmit FIFO Interface**

| Signal Name       | I/O | Description                                                                                                                                                                                                                    |

|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dma_tx_end_tog    | 0   | Toggled to indicate that a frame has been completed<br>and status is now valid on the $tx_r_status$ output.<br>Note that this signal is not activated when a frame is<br>being retried due to a collision.                     |

| dma_tx_status_tog | Ι   | This signal must be toggled each time either<br>dma_tx_end_tog or collision_occured are activated,<br>to indicate that the status has been acknowledged.<br>This asynchronous input is synchronized into the tx_clk<br>domain. |

| tx_r_status[3:0] | 0 | <ul> <li>[3]: fifo_underrun - status output indicating that the MAC transmitter has under run due to one of the following conditions. Data under run indicated by tx_r_underflow input from the external FIFO interface, status write back error due to status write back not completing when another status write back is attempted or a tx_r_err was driven on the external FIFO interface during the last frame transfer. Reset once dma_tx_status_tog changes logic state.</li> <li>[2]: collision_occured - HALF DUPLEX status output indicating that the frame in progress has suffered a collision and that re-transmission of the frame should take place. Set when the collision occurs and reset once dma_tx_status_tog changes logic state. Note that dma_tx_end_tog is not activated.</li> <li>[1]: late_coll_occured - HALF DUPLEX status output indicating that the frame in progress suffered a late collision and was aborted. Valid when dma_tx_end_tog changes logic state.</li> <li>[0]: too_many_retries - HALF DUPLEX status output indicating that the frame in progress experienced are a collision and was aborted. Valid when dma_tx_end_tog changes logic state.</li> </ul> |

|------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |   | excess collisions and was aborted. Valid when<br>dma_tx_end_tog changes logic state. Cleared once<br>dma_tx_status_tog changes logic state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## **External Receive FIFO Interface**

| Note: | Receive FIFO interface of | outputs are synchronize | ed to the <i>rx_clk</i> clock domain. |

|-------|---------------------------|-------------------------|---------------------------------------|

|       |                           |                         |                                       |

| Signal Name      | I/O | Description                                                                                                                                                                                                                                                                                         |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rx_w_wr          | 0   | Single rx_clk clock cycle wide active high output indicating a write to the external FIFO interface.                                                                                                                                                                                                |

| rx_w_data[127:0] | 0   | Received data for output to the external FIFO<br>interface, either 32-bit, 64-bit or 128-bit depending on<br>dma_bus_width[2:0] which is configured through the<br>register interface. This output is only valid when<br>rx_w_wr is high.                                                           |

| rx_w_sop         | 0   | Start of packet, indicates the word output to the external FIFO interface is the first in a packet. This output is only valid when rx_w_wr is high.                                                                                                                                                 |

| rx_w_eop         | 0   | End of packet, indicates the word output to the<br>external FIFO interface is the last in a packet. This<br>output is only valid when rx_w_wr is high. (Note this<br>signal will not be asserted if the receive path is<br>disabled during frame reception however rx_w_flush<br>will be asserted.) |

| rx_w_status[44:0] | 0 | Status signals, valid with rx_w_eop (with the                                                                                |

|-------------------|---|------------------------------------------------------------------------------------------------------------------------------|

|                   |   | exception of bits 20:15, which are valid on                                                                                  |

|                   |   | both rx_w_sop and rx_w_eop), definitions as                                                                                  |

|                   |   | follows:                                                                                                                     |

|                   |   | <ul> <li>[44] - rx_w_code_error indicates a code error.</li> <li>[43] - rx w too long indicates the frame was too</li> </ul> |

|                   |   |                                                                                                                              |

|                   |   | long.<br>[42] - rx_w_too_short indicates the frame was too                                                                   |

|                   |   | short.                                                                                                                       |

|                   |   | [41] - rx_w_crc_error indicates the frame had a bad                                                                          |

|                   |   |                                                                                                                              |

|                   |   | [40] - rx_w_length_error indicates the length field                                                                          |

|                   |   | was checked and was incorrect.                                                                                               |

|                   |   | [39] - rx w snap match indicates the frame was                                                                               |

|                   |   | SNAP encoded and had either no VLAN tag or a                                                                                 |

|                   |   | VLAN tag with the CFI bit not set.                                                                                           |

|                   |   | [38] - rx_w_checksumu indicates the UDP checksum                                                                             |

|                   |   | was checked and was correct.                                                                                                 |

|                   |   | [37] - rx_w_checksumt indicates the TCP checksum                                                                             |

|                   |   | was checked and was correct.                                                                                                 |

|                   |   | [36] - rx_w_checksumi indicates the IP checksum                                                                              |

|                   |   | was checked and was correct.                                                                                                 |

|                   |   | [35] - rx_w_type_match4, indicates the received                                                                              |

|                   |   | frame was matched on type ID register 4.                                                                                     |

|                   |   | [34] - rx_w_type_match3, indicates the received                                                                              |

|                   |   | frame was matched on type ID register 3.                                                                                     |

|                   |   | [33] - rx_w_type_match2, indicates the received frame was matched on type ID register 2.                                     |

|                   |   | [32] - rx_w_type_match1, indicates the received                                                                              |

|                   |   | frame was matched on type ID register 1.                                                                                     |

|                   |   | [31] - rx w add match4, indicates the received                                                                               |

|                   |   | frame was matched on specific address register 4.                                                                            |

|                   |   | [30] - rx w add match3, indicates the received                                                                               |

|                   |   | frame was matched on specific address register 3.                                                                            |

|                   |   | [29] - rx w add match2, indicates the received                                                                               |

|                   |   | frame was matched on specific address register 2.                                                                            |

|                   |   | [28] - rx_w_add_match1, indicates the received                                                                               |

|                   |   | frame was matched on specific address register 1.                                                                            |

|                   |   | [27] - rx_w_ext_match4, indicates the received                                                                               |

|                   |   | frame was matched externally by the ext_match4                                                                               |

|                   |   | input pin.                                                                                                                   |

|                   |   | [26] - rx_w_ext_match3, indicates the received                                                                               |

|                   |   | frame was matched externally by the ext_match3                                                                               |

|                   |   | input pin.                                                                                                                   |

|                   |   | [25] - rx_w_ext_match2, indicates the received                                                                               |

|                   |   | frame was matched externally by the ext_match2                                                                               |

|                   |   | input pin.                                                                                                                   |

|                   |   | [24] - rx_w_ext_match1, indicates the received<br>frame was matched externally by the ext_match1                             |

|                   |   | input pin.                                                                                                                   |

|                   |   | [23] - rx w uni hash match, indicates the received                                                                           |

|                   |   | frame was matched as a unicast hash frame.                                                                                   |

|                   |   | [22] - rx_w_mult_hash_match, indicates the                                                                                   |

|                   |   | received frame was matched as a multicast hash                                                                               |

|                   |   | frame.                                                                                                                       |

|                   |   | [21] - rx_w_broadcast_frame, indicates the                                                                                   |

|                   |   |                                                                                                                              |

|                         |   | <pre>received frame is a broadcast frame. [20] - rx_w_prty_tagged, indicates a VLAN priority tag detected with received packet. [19:16] - rx_w_tci[3:0], indicates VLAN priority of received packet. [15] - rx_w_vlan_tagged, indicates VLAN tag detected with received packet. [14] - rx_w_bad_frame, indicates received packet is bad. [13:0] - rx_w_frame_length, indicates number of bytes in received packet.</pre> |

|-------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| add_match_vec[32:<br>5] | 0 | If the GEM is configured to support 32 specific<br>address match registers then these outputs indicate<br>matches for specific address registers 5 to 32.<br>Matches for registers 1 to 4 are indicated in the<br>rx_w_status vector described above.                                                                                                                                                                    |

| rx_w_mod[3:0]           | 0 | Write module, indicates how many bytes are valid on<br>rx_w_data during the last transfer of the packet:<br>0000- all bytes are valid<br>0001 - rx_r_data[7:0] is valid<br>0010 - rx_r_data[15:0] is valid<br>0011 - rx_r_data[23:0] is valid, and so on until<br>1111 - rx_r_data[119:0] is valid<br>This output is only valid when coincident with both<br>rx_w_wr and rx_w_eop being high.                            |

| rx_w_err                | 0 | Error, active high output indicating the current packet contains an error. This signal is only valid when rx_w_wr is active high and may be set at any time during packet transfer.                                                                                                                                                                                                                                      |

| rx_w_overflow           | I | FIFO overflow, indicates to the MAC that the external RX FIFO has overflowed. The MAC uses this signal for status reporting at the end of frame.                                                                                                                                                                                                                                                                         |

| rx_w_flush              | 0 | FIFO flush, active high output indicating that the external RX FIFO should be cleared. This signal is set when the receive path is disabled.                                                                                                                                                                                                                                                                             |

## AMBA (APB) Interface

| Signal Name | I/O | Description                                                                                                                                                                                |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| n_preset    | I   | Active low AMBA reset (nPRESET). This signal must be<br>asserted low asynchronously, and deasserted high<br>synchronously with pclk. Resets all APB registers and the<br>pclk_syncs block. |

| pclk        | Ι   | Peripheral bus clock (PCLK).                                                                                                                                                               |

| psel         | Ι | Peripheral select (PSEL). Active high select signal to indicate that a valid access is being made to one of the GEM's registers.                                                                                                                                 |

|--------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| penable      | - | Peripheral enable (PENABLE). This indicates the second clock cycle of an access and indicates that the write data may be strobed into a register on the next rising edge of pclk, or that the read data is expected to be valid at the next rising edge of pclk. |

| pwrite       | Ι | Peripheral write strobe (PWRITE). This indicates that a write access is taking place (if psel is active).                                                                                                                                                        |

| paddr[9:2]   | Ι | Address bus from selected master (PADDR). Indicates which register is being accessed. This address is word-aligned within the GEM and therefore should be connected to bits [09:02] of the APB address bus.                                                      |

| pwdata[31:0] | Ι | Write data. Data to be written into the addressed register.                                                                                                                                                                                                      |

| prdata[31:0] | 0 | Read data. Data read from the addressed register. For APB Rev 2.0, it is driven to logic 0 when not addressed.                                                                                                                                                   |

| perr         | 0 | Indicates an APB access to an invalid address. Should be sampled when penable is high. This signal is optional and not a standard AMBA signal.                                                                                                                   |

## AMBA (AHB) Interface

| Signal Name   | I/O | Description                                                                                                                                 |

|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| n_hreset      | I   | Active low asynchronous reset for the DMA. This signal must be asserted low asynchronously and deasserted high synchronously with hclk.     |

| hclk          | I   | AHB bus clock.                                                                                                                              |

| hready        | Ι   | Slave device drives this low to extend data phase.                                                                                          |

| hresp[1:0]    | I   | Slave response, 00 for OK, any other response is not<br>OK and triggers an interrupt. AMBA split and retry<br>operations are not supported. |

| hgrant        | Ι   | AHB bus grant.                                                                                                                              |

| haddr[31:0]   | 0   | AHB address.                                                                                                                                |

| htrans[1:0]   | 0   | AHB transfer type as follows:<br>00 - Idle<br>01 - Busy (not used by the GEM)<br>10 - Non-sequential<br>11 - Sequential.                    |

| hwrite        | 0   | High for AHB write, low for AHB read.                                                                                                       |

| hrdata[127:0] | I   | Data read from memory, configurable for 32 bit, 64 bit<br>or 128 bit bus widths. Unused bits should be tied to<br>logic 0 or logic 1.       |

| hsize[2:0]    | 0 | Transfer size, configured according to AMBA AHB<br>data bus width as follows:<br>010 - 32 bit transfers<br>011 - 64 bit transfers<br>100 - 128 bit transfers. |

|---------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hburst[2:0]   | 0 | Burst type, 000 for single transfer, 001 for incrementing burst and 011 for four beat incrementing burst.                                                     |

| hprot[3:0]    | 0 | Protection type. Parameterizable via<br>`gem_hprot_value                                                                                                      |

| hwdata[127:0] | 0 | Data written to memory, configurable for 32 bit, 64 bit or 128 bit bus widths.                                                                                |

| hbusreq       | 0 | AHB bus request.                                                                                                                                              |

| hlock         | 0 | Always asserted with hbusreq to lock the grant. This signal may be left unconnected if required (refer to user guide section 2)                               |

## AMBA (AXI4) Interface

| Signal Name   | I/O | Description                                                                                                                                              |

|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| n_areset      | I   | Active low asynchronous reset for the DMA. This signal must be asserted low asynchronously and deasserted high synchronously with aclk.                  |

| aclk          | Ι   | AXI bus clock.                                                                                                                                           |

| awaddr [31:0] | 0   | AXI write channel address.                                                                                                                               |

| awlen[7:0]    | 0   | AXI write channel burst length. Maximum value is 15.<br>Bits 7:4 are tied low.                                                                           |

| awsize[2:0]   | 0   | Transfer size, configured according to AXI data bus<br>width as follows:<br>010 - 32 bit transfers<br>011 - 64 bit transfers<br>100 - 128 bit transfers. |

| awburst[1:0]  | 0   | All bursts generated by the AXI DMA are incrementing, so this output is tied to 2'b01.                                                                   |

| awvalid       | 0   | AXI write request.                                                                                                                                       |

| awready       | Ι   | AXI write request accepted by slave.                                                                                                                     |

| awid[3:0]     | 0   | Not currently used by the GEM DMA. This output is tied low.                                                                                              |

| awcache[3:0]  | 0   | Cache support. Parameterizable via `<br>`gem_axi_cache_value                                                                                             |

| awlock[1:0]   | 0   | Not currently used by the GEM DMA. This output is tied low.                                                                                              |

| awprot[2:0]   | 0   | Protection unit support. Parameterizable via `<br>`gem_axi_prot_value                                                                                    |

| wdata[63:0]  | 0 | Data write to memory, configurable for 32 bit, or 64 bit bus widths. Unused bits are tied to logic 0.                                                    |

|--------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| wlast        | 1 | Identifies the last data of a burst.                                                                                                                     |

| wvalid       | 0 | AXI write data valid.                                                                                                                                    |

| wready       | I | AXI write data accepted by slave.                                                                                                                        |

| bresp[1:0]   | 1 | Slave response, 00 for OK, any other response is not OK and triggers an interrupt.                                                                       |

| bid[3:0]     |   | Not currently used by the GEM DMA.                                                                                                                       |

| bvalid       | 1 | AXI write response bus valid.                                                                                                                            |

| bready       | 0 | AXI write response accepted.                                                                                                                             |

| araddr[31:0] | 0 | AXI read channel address.                                                                                                                                |

| arlen[7:0]   | 0 | AXI read channel burst length. Maximum value is 15.<br>Bits 7:4 are tied low.                                                                            |

| arsize[2:0]  | 0 | Transfer size, configured according to AXI data bus<br>width as follows:<br>010 - 32 bit transfers<br>011 - 64 bit transfers<br>100 - 128 bit transfers. |

| arburst[1:0] | 0 | All bursts generated by the AXI DMA are incrementing, so this output is tied to 2'b01.                                                                   |

| arvalid      | 0 | AXI read request.                                                                                                                                        |

| arready      | I | AXI read request accepted by slave.                                                                                                                      |

| arid[3:0]    | 0 | Not currently used by the GEM DMA. This output is tied low.                                                                                              |

| arcache[3:0] | 0 | Cache support. Parameterizable via `<br>`gem_axi_cache_value                                                                                             |

| arlock[1:0]  | 0 | Not currently used by the GEM DMA. This output is tied low.                                                                                              |

| arprot[2:0]  | 0 | Protection unit support. Parameterizable via `<br>`gem_axi_prot_value                                                                                    |

| rdata[127:0] | I | Data read from memory, configurable for 32 bit, 64 bit<br>or 128 bit bus widths. Unused bits should be tied to<br>logic 0 or logic 1.                    |

| rlast        | I | Identifies the last data of a read burst.                                                                                                                |

| rresp[1:0]   | I | Slave response, 00 for OK, any other response is not OK and triggers an interrupt.                                                                       |

| rid[3:0] | I | Not currently used by the GEM DMA. |

|----------|---|------------------------------------|

| rvalid   | I | AXI read data valid                |

| rready   | 0 | AXI read data accepted             |

#### **Transmit Packet Buffer Memory Interface**

Port A of the transmit packet memory should be clocked on hclk/aclk and port B should be clocked on  $tx_clk$ .

| Signal Name        | I/O | Description                                                                                                        |

|--------------------|-----|--------------------------------------------------------------------------------------------------------------------|

| txdpram_ena        | 0   | Transmit packet buffer memory Port A chip select                                                                   |

| txdpram_wea        | 0   | Transmit packet buffer memory Port A write enable (always high)                                                    |

| txdpram_addra[N:0] | 0   | Transmit packet buffer memory Port A word address bus. Address width configurable.                                 |

| txdpram_dia[63:0]  | 0   | Transmit packet buffer memory Port A write data bus.<br>Either 32-bit or 64-bit depending on<br>dma_bus_width[2:0] |

| txdpram doa[63:0]  | I   | Transmit packet buffer memory Port A read data bus (not used by design – now removed from top level)               |

| txdpram enb        | 0   | Transmit packet buffer memory Port B chip select                                                                   |

| txdpram web        | 0   | Transmit packet buffer memory Port B write enable (always low)                                                     |

| txdpram_addrb[N:0] | 0   | Transmit packet buffer memory Port B word address bus. Address width configurable.                                 |

| txdpram dib[63:0]  | 0   | Transmit packet buffer memory Port B write data bus (not used by design – now removed from top level)              |

| txdpram_dob[63:0]  | I   | Transmit packet buffer memory Port B read data bus.<br>Either 32-bit or 64-bit depending on<br>dma_bus_width[2:0]  |

#### **Receive Packet Buffer Memory Interface**

Port A of the receive packet memory should be clocked on  $rx_clk$  and port B should be clocked on hclk/aclk.

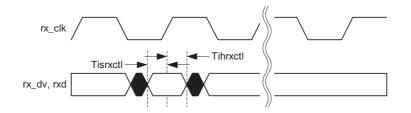

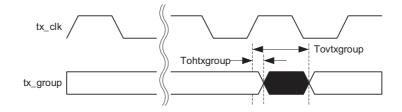

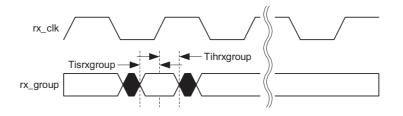

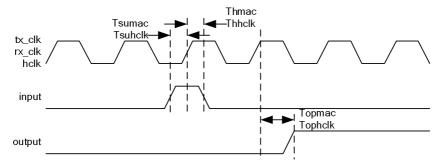

| Signal Name        | I/O | Description                                                                       |  |